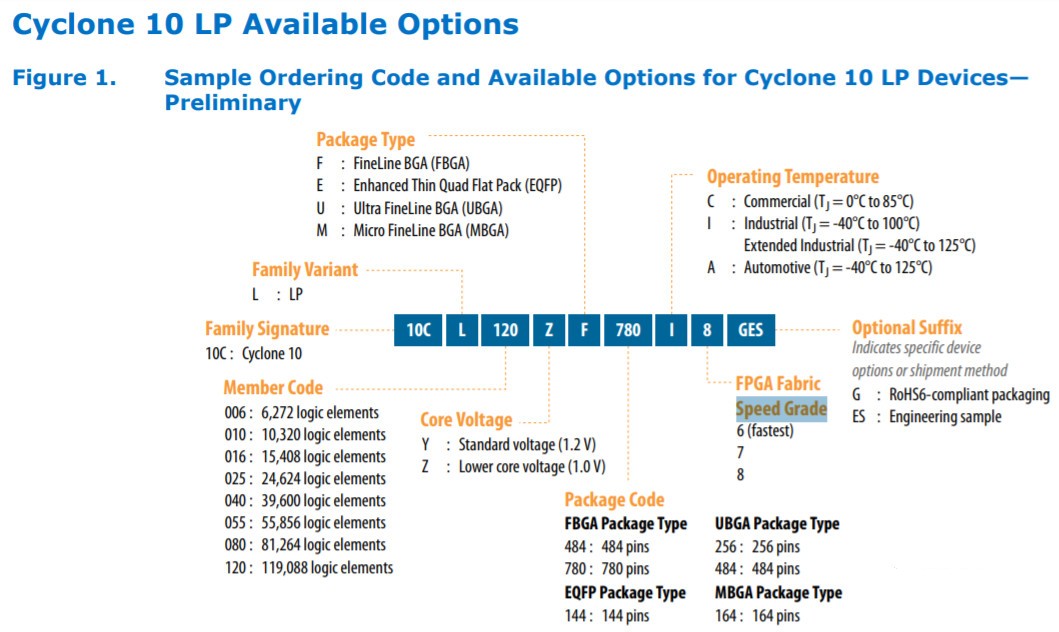

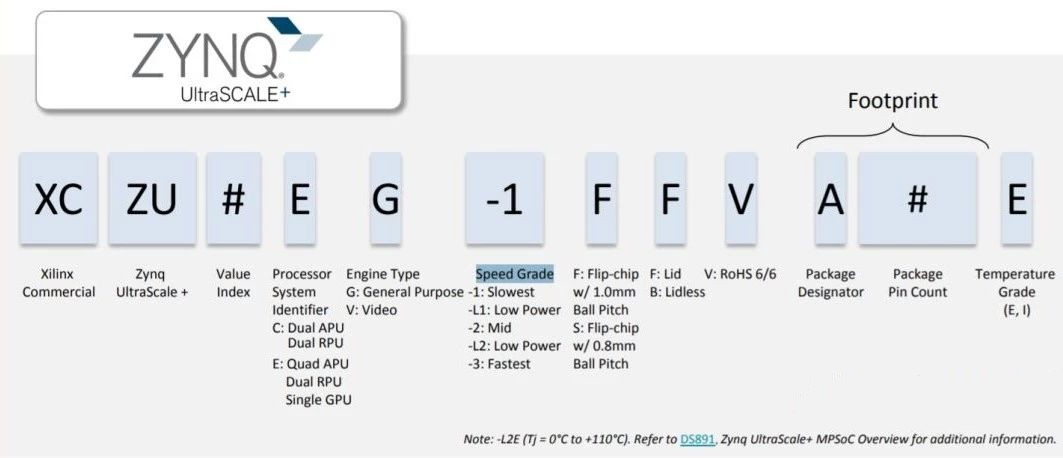

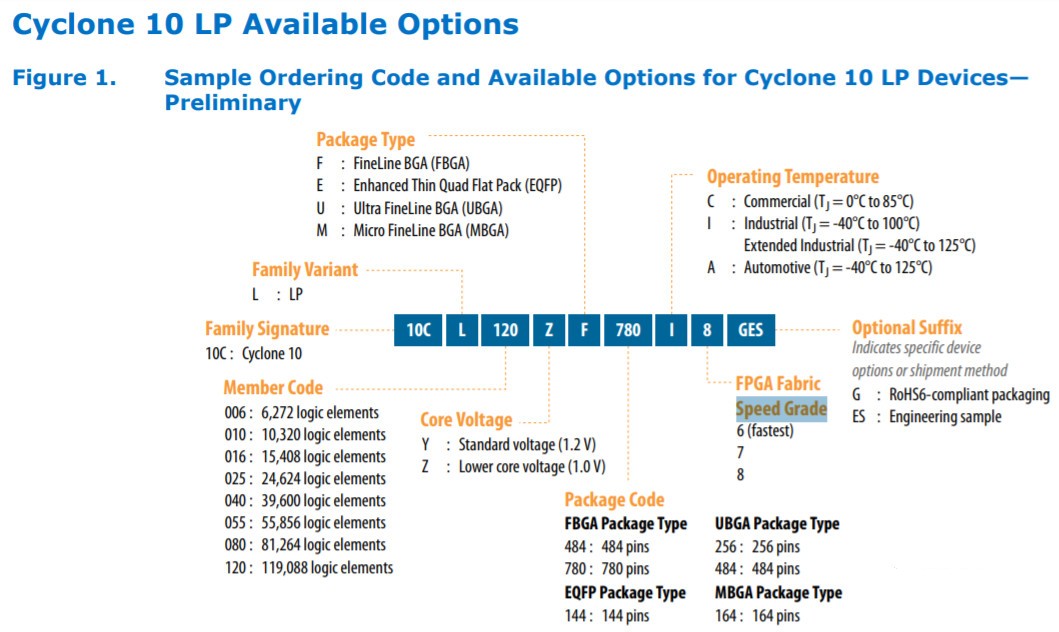

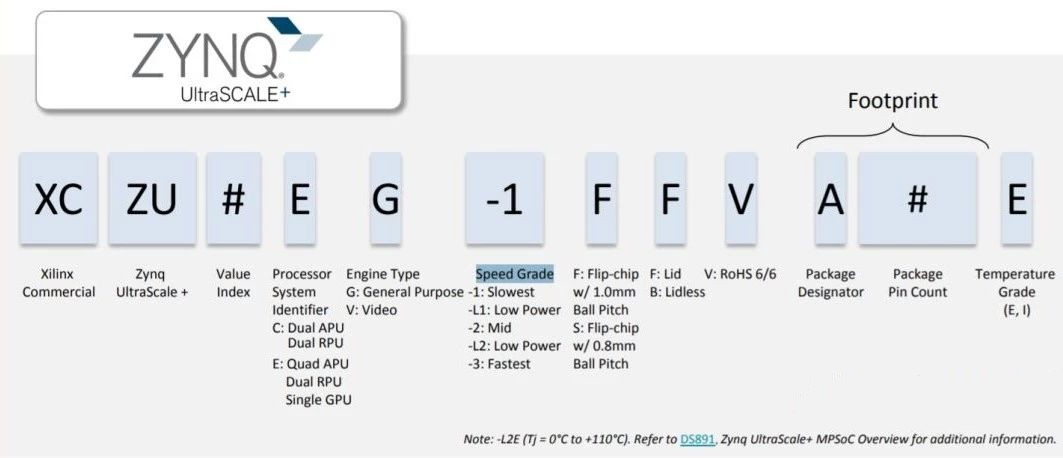

FPGA Series "Speed Grade"

Time:2024-01-08

Views:626

Everyone will see a parameter when making FPGA selections: Speed Grade, which is the speed grade of the chip.

The speed grade of the chip is not specially designed, but is actually tested and calibrated after the chip is produced; the ratio of fast chips in the total production is low, and the price is correspondingly high.

"The lower the serial number, the higher the speed grade" is the sorting method for Altera FPGAs, and "the higher the serial number, the higher the speed grade" is the sorting method for Xilinx FPGAs.

*The speed class of a chip is determined by the gate delay and line delay inside the chip, which in turn depend on the length of the transistor, L, and the capacitance, C. The difference between these two values ultimately depends on the production process of the chip.

*In the chip production process, there is a stage called speed binning, where the chips are screened and categorized according to a set of criteria and then classified into different speed grades.

*The calibration of speed binning not only depends on the quality of the chip itself, but also has a great relationship with the market positioning of the chip, and the probability of repair and cost is also one of the factors.

*The grade of the chip can be specifically adjusted and improved after testing, and this technique is widely used in the production of memory chips.

*The process of chip production is full of all kinds of variables, the production process can be controlled, but the control can not be accurate to a molecule, an atom, product quality can only be a statistical target. Chips on the same wafer can vary, even in different parts of the same chip. The speed grade is a statistic that reflects certain common characteristics of a batch of chips and does not represent the quality of individual chips. Also, since some chips are tested on a sample basis, it cannot be ruled out that the individual performance of an individual chip may be lower than the calibrated speed grade. However, the testing of FPGAs is extremely rigorous, and it is likely that every chip we get our hands on has been exhaustively tested. This is why FPGA chips cost more than regular chips.

* The vast majority of chips in the same class should perform above the speed grade classification. This is also the reason why FPGA designs with a few timing analysis violations are still able to function properly when downloaded to the chip (the model parameters used for timing analysis are the statistical parameters of the chip, which are the most conservative and safest). However, due to the same level of the chip there are still performance differences, there are timing violations but a single test success of the FPGA design can not ensure that the mass production does not have problems on individual chips (problems have to be returned to the repair or on-site investigation, the cost of all of a sudden went up). Therefore, it is still necessary to converge the timing to be assured of mass production, which is the engineering standards for product quality assurance.

* The real world is analog, not digital. When examining the reality of the problem, digital engineers and software engineers should abandon the concept of "one is one, zero is zero", with a continuous vision of the real world of continuous change.

* Chip production process uncertainty led to the chip performance differences, this difference affects the price of the chip, the price and performance of the trade-off affects the FPGA design engineers in the device selection, design method of decision-making, the production of cost-effective products to determine the sales of the product, product sales and determine the chip purchasing volume, the purchasing volume affects the purchase price of the chip ...

The selection of device speed grade, a basic principle is: in the case of meeting the application requirements, try to use a device with a low speed grade, the main benefits are as follows:

1. Due to the transmission line effect, the speed grade of the device is more likely to produce signal reflection, the design should be in the signal integrity to spend more energy;

2. high speed grade devices are generally used less, the price will often increase exponentially, and high-speed device supply channels are generally less, device ordering cycle is generally longer, will extend the product development cycle, reduce the product launch rate.